Application Note

April 1998

AN9641.1

## Introduction

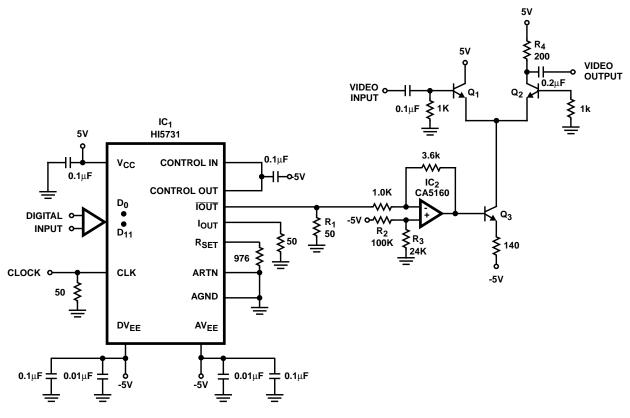

You can use variable-gain amplifiers (VGAs) in many types of systems, such as radio receivers, in which the input signal voltage depends on an uncontrolled variable, such as distance to the transmitter. In this type of system, you can use a VGA to ensure that the input signal amplitude matches the input voltage range of key components, such as ADCs and DACs, thereby maximizing the converters' dynamic range. The VGA in Figure 1 has high bandwidth, ranging from 115MHz at high gain to 225MHz at low gain, so you can use this circuit in the RF-signal path without degrading the signal. You can update the DAC in this circuit at 100MHz, but the level-shifter op amp limits the speed at which you can update the gain of the VGA to 3MHz. As configured, this VGA implements a calibration function with a 3MHz DAC update rate.

The VGA design comprises a three-transistor, long-tailed pair configuration comprising  $Q_1$ ,  $Q_2$ , and  $Q_3$ . By changing the base voltage of  $Q_3$ , the DAC (IC<sub>1</sub>) varies the emitter currents of the long-tailed pair. Changing  $Q_3$ 's base voltage controls the gain according to the following equation, where K is a function of the emitter current and  $V_{B3}$  is the base voltage of  $Q_3$ :

$G = KV_{IN}|V_{B3}|.$

The gain control and bias-stability parameters of the circuit depend on transistor matching, so the circuit uses an HFA3102 matched, long-tailed array for Q<sub>1</sub> through Q<sub>3</sub>. The usable range of V<sub>B3</sub> is -0.8 to -4.4V, which corresponds to a gain range of 11.8 to -16.9dB, respectively. This gain span is a total of 28.7dB. The gain is proportional to R<sub>4</sub>. Increasing R<sub>4</sub> increases the gain, but the gain span stays constant at approximately 28.7dB. Increasing the gain causes a corresponding decrease in the frequency response.

$R_2, R_3$ , and the -5V supply form a bias circuit that sets  $V_{B3}$  to -4.4V when there is no DAC output current (the voltage across  $R_1$  is zero), which occurs at a digital input of all ones. When the digital input is all zeros, the DAC output current is 20mA, which develops -1V across  $R_1$ . IC<sub>2</sub> level-shifts and amplifies this voltage to yield  $V_{B3}$  = -0.8V. The CA5160 works well as the level shifter because its low bias currents do not affect the DC performance, and its bandwidth enables the gain to change at a rate as high as 3MHz.

You should keep the video input signal level at about 25mV to prevent distortion. The signal path has an excellent frequency response because the HFA3102 is the only component in the signal path. A frequency response plot for  $V_{B3} = -3V$  (gain of 10dB) shows that the transfer function is well-behaved with no peaking and that the frequency response is 131MHz at the -3dB point. The DAC transfers the digital input to the internal registers on the rising edge of the clock pulses. This circuit uses the inverting DAC output to yield a positive increasing-transfer function, but you can obtain the inverse-transfer function by using the noninverting input (Table 1).

|  | TABLE 1. | VGA | PERF | ORMA | NCE | SUMMARY | 1 |

|--|----------|-----|------|------|-----|---------|---|

|--|----------|-----|------|------|-----|---------|---|

| PARAMETER                            | MINIMUM        | MAXIMUM        |

|--------------------------------------|----------------|----------------|

| Gain (dB)                            | -16.9          | 11.8           |

| V <sub>B3</sub> (V)                  | -4.4           | -0.8           |

| F <sub>-3dB</sub> (MHz)              | 225            | 115            |

| Digital Input/Inverting<br>Output    | 0000 0000 0000 | 1111 1111 1111 |

| Digital Input/Noninverting<br>Output | 1111 1111 1111 | 0000 0000 0000 |

If fast updates are unnecessary, you can use a slower DAC than  $IC_1$ . However, you may also have to redesign the interface circuit ( $IC_2$  and associated components) if the DAC output voltage swing changes.

NOTE:

1. Q<sub>1</sub>, Q<sub>2</sub>, Q<sub>3</sub> = HFA3102.

FIGURE 1.

This variable-gain amplifier has high bandwidth ranging from 115MHz at high gain to 225MHz at low gain, and you can update the gain at a 3MHz rate.

All Intersil semiconductor products are manufactured, assembled and tested under ISO9000 quality systems certification.

Intersil semiconductor products are sold by description only. Intersil Corporation reserves the right to make changes in circuit design and/or specifications at any time without notice. Accordingly, the reader is cautioned to verify that data sheets are current before placing orders. Information furnished by Intersil is believed to be accurate and reliable. However, no responsibility is assumed by Intersil or its subsidiaries for its use; nor for any infringements of patents or other rights of third parties which may result from its use. No license is granted by implication or otherwise under any patent or patent rights of Intersil or its subsidiaries.

For information regarding Intersil Corporation and its products, see web site www.intersil.com